平本・小林研究室

シリコン半導体の性能を極限まで追究するシリコンデバイスの研究室です.主なテーマは,今後さらなる発展が期待される下記の2つに大別されます.(1) 大規模集積シリコン微細MOSトランジスタ

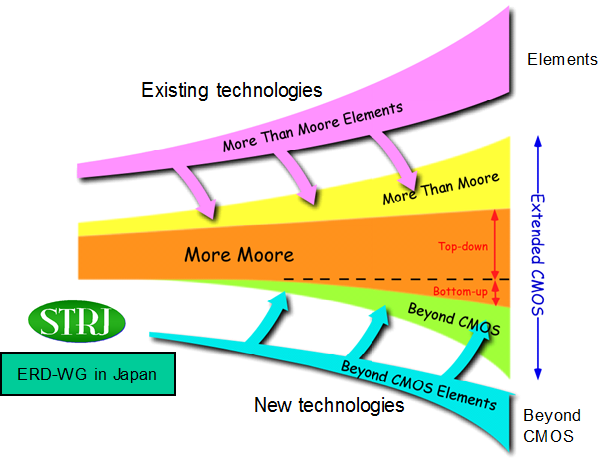

研究ターゲットは,各種機能が融合した「Extended CMOS」と呼ぶべき究極の集積デバイスです. Extended CMOS実現に向けて,超低電力トランジスタ技術[1],微細トランジスタのランダム特性ばらつき[2],極微細シリコンナノワイヤトランジスタ[3],新機能シリコン単電子トランジスタ,およびそれらの集積化の研究を行っています. 図1は,従来のトランジスタ微細化・高性能化を中心とするMore Moore技術をベースに,さまざまな機能が融合してExtended CMOSが広がっていく様子を表しています.

(2) 高耐圧シリコンパワートランジスタ

SiCやGaNなどの研究が進展するパワーデバイスの分野でも,シリコンデバイスはさらなる性能向上が可能であると私たちは考えています. IGBTと呼ばれるパワートランジスタのスケーリング[4]や両面ゲート化[5]に加え,オン抵抗を大幅に低減可能な横型パワーMOSFETの設計にも着手しました[6].

将来的には,(1)と(2)も融合したCMOS/パワーデバイス集積エレクトロニクスも模索しています. 高度情報化社会およびカーボンニュートラルの基盤となる半導体の主役は,今後もシリコンおよびCMOS技術であると私たちは考えています.

図1. Extended CMOSの概念図.国際半導体ロードマップ(ITRS)に掲載されている.

[1] A. Ueda et al., “Ultra-Low Voltage (0.1V) Operation of Vth Self-Adjusting MOSFET and SRAM Cell”, VLSI Symposium on Technology, pp. 198 - 199, June, 2014.

[2] T. Mizutani et al, “Analysis of Transistor Characteristics in Distribution Tails beyond ±5.4σ of 11 Billion Transistors”, IEDM, pp. 826 - 829, December, 2013.

[3] H. Qiu et al., “Statistical Analyses of Random Telegraph Noise Amplitude in Ultra-Narrow (Deep Sub-10nm) Silicon Nanowire Transistors”, Symposium on VLSI Technology, pp. T50 - T51, June, 2017.

[4] T. Saraya et al, “Demonstration of 1200V Scaled IGBTs Driven by 5V Gate Voltage with Superiorly Low Switching Loss”, IEDM, pp. 189 - 192, December, 2018.

[5] T. Saraya et al., “3.3 kV Back-Gate-Controlled IGBT (BC-IGBT) Using Manufacturable Double-Side Process Technology”, IEDM, pp. 87 - 90, December, 2020.

[6] Patent filed, 2021.

ホーム-->